Input Output Device에는 각각의 Register가 들어있다. 이 register에 접근하여 원하는 정보를 얻어올 수 있다.

Configuration Register ( Initiate 를 담당 ), Data Register, Status Register ( IO Device의 상태를 기억 )

UART : Universal Asynchronous Receiver and Transmitter

비동기방식 -> Clock이 필요없다, Full-duplex(전이중) 방식 통신 -> 동시에 송 수신이 가능하다.

Asynchronous이기 때문에 Agreement가 필요하다 ( Protocol ) : 언제 보낼지, 어떤 형식으로 보낼지, 얼마나 빠르게 보낼지

Transmitter의 Data Format : UART의 전송형식

전송형식은 StartBit + Data + ( Parity Bit : 오류검사 ) + Stop Bit으로 구성된다.

StartBit이 0으로 바뀌면 전송시작. 8Bit의 Data Bit 또는 7 Data Bit + 1 Parity Bit을 전송. 마지막에 Stop Bit.

전송과정에서 Clock은 필요없다.

Receiver

Start Bit이 0이 된 것을 감지 -> 각각의 1 Bit을 16등분한 뒤 중간 값을 가져온다. ( 16등분을 위해 Receiver는 Clock을 필요로 한다. )

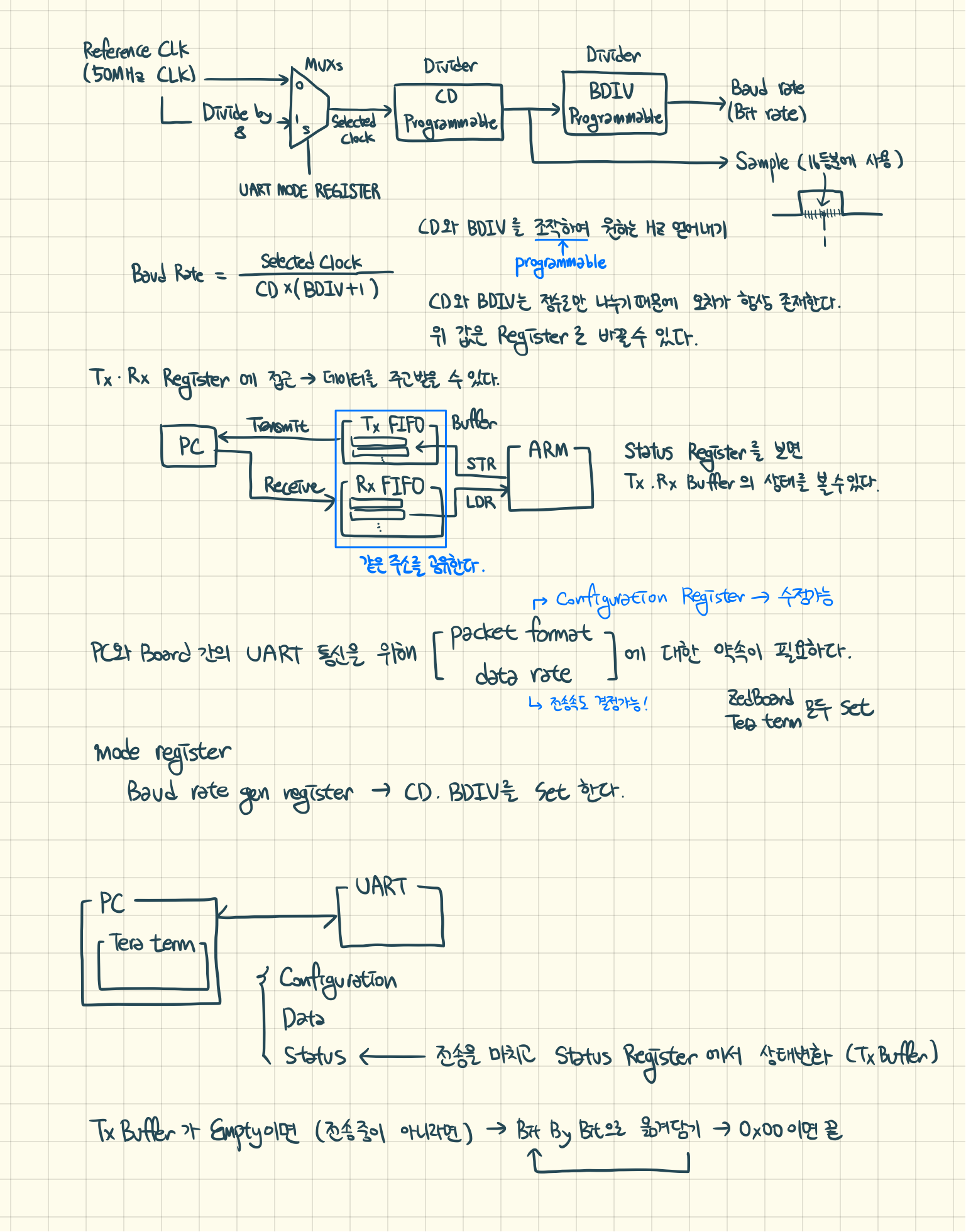

UART Module

Tx, Rx Register에 접근하여 데이터를 주고받을 수 있다.

Status Register에 값을 입력하여 Protocol을 설정할 수 있다. - PC의 수신자와 Protocol을 일치시켜줘야 데이터를 정상수신한다.

Baud Rate = Selected_Clock / ( CD * ( BDIV + 1 )) : CD, BDIV 값을 수정하여 원하는 Rate를 얻을 수 있다.

Tx, Rx의 Status Register를 보면 Buffer의 상태도 파악가능하다.

특이하게, Tx와 Rx는 같은 메모리주소를 공유한다. -> 입력하면 송신, 읽어오면 수신의 역할을 하는 메모리

CPU와 UART사이의 연결 중 Control information에 따라 어느 Register에 접근할 지 결정 ( 같은 주소 두 개의 공간 )

전송은 Tx Buffer가 Empty한 상태를 유지할 때 까지 ( 모든 값을 전송할 때 까지 ) Bit By Bit으로 PC에 전송한다.

// 이 시리즈의 글들은 고려대학교의 Computer System Design 과목 ( COSE321 ) 을 수강하며 제가 공부한 내용입니다.

// 노트필기를 바탕으로 정리하여 올리고 있으므로, 부정확한 정보가 있을 수도 있습니다.

// 추후에 종강을 하면 워터마크를 삽입한 최종노트 PDF를 첨부할 계획입니다.

'학부생 CS > 컴퓨터 시스템 설계' 카테고리의 다른 글

| Computer System Design - 7 : Thumb, Thumb2 (3) | 2019.05.20 |

|---|---|

| Computer System Design - 6 : Timer (0) | 2019.05.20 |

| Computer System Design - 4 : Memory Map (3) | 2019.04.06 |

| Computer System Design - 3 : Assembly instruction (0) | 2019.03.28 |

| ARM assembly 로 정수 정렬하기 (3) -반복문, Loop, Branch link (0) | 2019.03.23 |