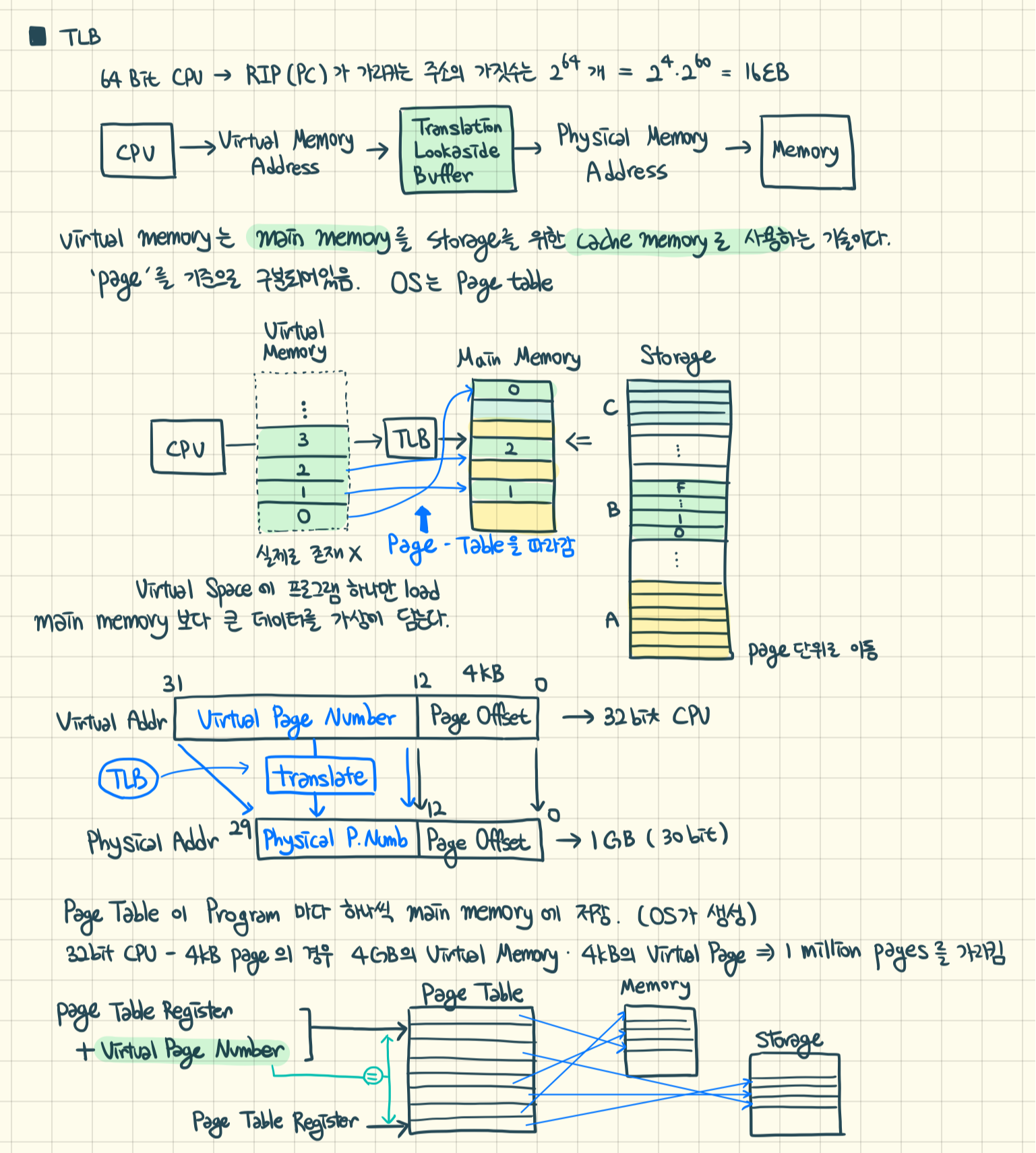

TLB - Translation Lookaside Buffer

TLB는 Virtual Memory Address를 Physical Memory Address로 전환하는 역할을 하는 장치.

TLB가 필요한 이유

Virtual Memory는 Main Memory를 Storage의 Cache Memory로 사용하는 기술이다.

[ CPU - Cache Memory - Main Memory ]

[ CPU - Main Memory - Storage Memory ]

두 순서가 같은 관계로 구성되도록 하는 기술이 Virtual Memory이다.

64Bit CPU를 이용하는 경우, Register가 가질 수 있는 주소의 길이는 2^64 = 2^4 x 2^60 = 16EB ( 1 EB = 1,000,000 TB )

Virtual Address & TLB의 작동방식

Storage에서 파일을 읽어올 때는 'Page'를 단위로 값을 가져온다.

여러가지 프로그램을 동시에 실행시킨다고 할 때, Main Memory에는 Storage에 저장되어 있는 여러 프로그램의 일부분이 올라가 저장되어있겠지만, Virtual Memory에는 단 하나의 프로그램만이 저장되어있다고 생각할 수 있다. ( 물론 Virtual Memory는 말 그대로 가상의 메모리이기에 존재하지는 않는다. ) CPU가 접근하는 Virtual Memory에는 데이터가 순서대로 저장되어있고, 이 Memory에 Virtual Address로 접근하고자 하면 TLB가 Physical Memory로 바꿔 Main Memory에서 필요한 값을 찾아준다.

Page - Table : Page Table이란, Virtual Address와 Physical Address를 연결시키는 Table로, OS가 알아서 만들어준다. 프로그램마다 하나씩 만들어져 Main Memory에 저장되어있으며, TLB에 의해 Virtual Address를 Physical로 바꾸는 작업을 할 때 마다 그 프로그램의 Table을 참고해 변환시켜준다.

32Bit CPU에서 4KB를 처리단위인 Page로 가지는 경우에, 4GB의 Virtual Memory를 가지고, 이를 4KB의 Virtual Page를 한 단위로 하여 처리한다. ( 이는 10만개의 Pages 에 해당한다. )

만약 64Bit CPU라면..? Wow...

- TLB의 작동

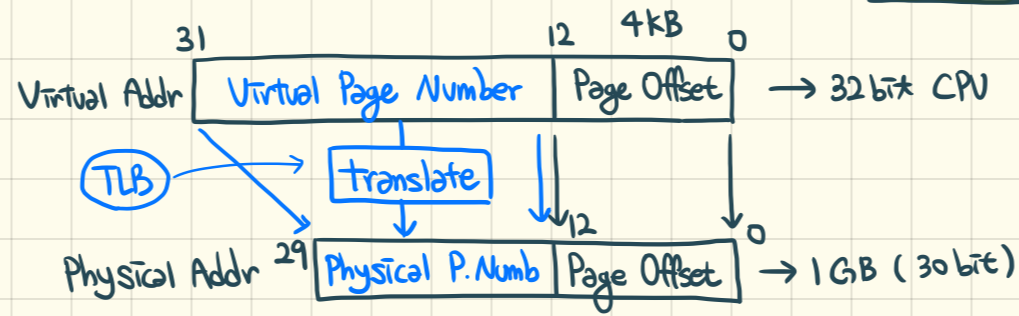

TLB의 작동방식에 대해 1GB의 Main Memory와 4KB의 Page 크기를 가지는 32Bit CPU를 기준으로 설명하겠다.

Virtual Address가 32Bit일 것이다. 1Bit당 1Byte를 의미하므로, 한 Page안에서의 위치를 나타낼 때는 아래 12Bit으로 나타내고, Page 끼리의 구분을 위해서는 뒤 20Bit을 사용할 것이다. 여기서 앞 12Bit을 'Page Offset'이라 부르고, 뒤 20Bit을 'Virtual Page Number'이라 칭한다.

실제 메모리가 1GB라면 주소를 30개의 Bit으로 표현할 수 있어야 한다. 그러나, Virtual Memory의 주소가 32Bit이므로, Virtual Address가 Physical Memory를 가리키기 위해서는 주소를 변환하는 작업을 필요로 한다. Virtual Memory의 앞 12Bit ( Page Offset ) 은 Main Memory에서도 Page안에서의 위치를 나타내기 위해 필요하므로 그대로 사용된다. 뒤의 20Bit ( Virtual Page Number ) 을 Physical Address ( Physical Page Number ) 에 맞추기 위해서 TLB를 사용하게 된다.

Page Table에서 Page Table Register가 해당 프로그램의 Page Table의 Base를 가리키고 있고, 여기에 Virtual Page Number를 더하면 ( 0번 ~ 2^20번 ) 해당 위치에는 Virtual Address가 접근하고자 하는 Physical Address가 저장되어있다. 이 주소를 이용해 Main Memory 또는 Storage에 접근할 수 있도록 하는 것이 TLB의 작동방식이다.

'학부생 CS > 컴퓨터 시스템 설계' 카테고리의 다른 글

| Computer System Design - 정리본.PDF (0) | 2019.07.07 |

|---|---|

| Computer System Design - 13 : TLB (2) (2) | 2019.07.07 |

| Computer System Design - 11 : Cache Memory 2 (0) | 2019.06.10 |

| Computer System Deisgn - 10 : Cache Memory (0) | 2019.05.28 |

| Computer System Design - 9 : IO Interrupt (0) | 2019.05.21 |